Harry H. Porter III Computer Science Department Portland State University

## **Abstract**

This document provides an overview of the BLITZ architecture and instruction set. The BLITZ microprocessor is designed specifically to support Computer Science education. The architecture is similar to contemporary RISC microprocessor architectures, but is simplified appropriately for student use. The BLITZ processor will normally be implemented by software emulation, although a hardware implementation of the CPU architecture presented here is also possible.

## **Basic Terminology**

In this document, we use the terms "byte", "halfword", "word", and "doubleword" to refer to various sizes of binary data.

|          | number   | number  |                                         |

|----------|----------|---------|-----------------------------------------|

|          | of bytes | of bits | example (in hex)                        |

| :        | ======   | ======  | ======================================= |

| byte     | 1        | 8       | A4                                      |

| halfword | 2        | 16      | C4F9                                    |

| word     | 4        | 32      | AB12CD34                                |

| doublewo | rd 8     | 64      | 01234567 89ABCDEF                       |

The bits within an 8-bit byte are numbered from 0 (least significant) to 7 (most significant).

The bits within a 16-bit halfword are numbered from 0 (least significant) to 15 (most significant).

The bits within a 32-bit word are numbered from 0 (least significant) to 31 (most significant).

The bits within a 64-bit doubleword are numbered from 0 (least significant) to 63 (most significant).

| 0    | 4    | 8    | 12   | 16   | 20   | <br>60  | 63  |

|------|------|------|------|------|------|---------|-----|

| ==== | ==== | ==== | ==== | ==== | ==== | ==      | ==  |

| 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | <br>0.0 | 0.0 |

A single hex digit can be used to represent 4 bits (half a byte, sometimes called a "nibble"), as follows.

| Binary | Нех |

|--------|-----|

| =====  | === |

| 0000   | 0   |

| 0001   | 1   |

| 0010   | 2   |

| 0011   | 3   |

| 0100   | 4   |

| 0101   | 5   |

| 0110   | 6   |

| 0111   | 7   |

| 1000   | 8   |

| 1001   | 9   |

| 1010   | Α   |

| 1011   | В   |

| 1100   | C   |

| 1101   | D   |

| 1110   | E   |

| 1111   | F   |

|        |     |

The 8 bits within a byte are conveniently expressed with two hex digits:

| 8-bit byte | In Hex |

|------------|--------|

|            | ====== |

| 1010 0100  | A4     |

The 32 bits in a word are given with 8 hex digits.

|           | 32-bit    | word      |           | In Hex   |

|-----------|-----------|-----------|-----------|----------|

|           |           |           |           | ======   |

| 1010 1011 | 0001 0010 | 1100 1101 | 0011 0100 | AB12CD34 |

The 64 bits (8 bytes) in a doubleword are conveniently expressed with 16 hex digits.

Other architectures use "quadwords" of 128 bits, but the BLITZ architecture does not provide instructions for manipulating quadword data.

## Memory

Main memory is byte addressable. Addresses are 4 bytes (i.e., 32 bits) long, allowing for up to 4 gigabytes to be addressed.

Memory can be viewed either as a sequence of bytes:

| address  | data     |

|----------|----------|

| (in hex) | (in hex) |

| ======   | ======   |

| 00000000 | 89       |

| 0000001  | AB       |

| 00000002 | CD       |

| 0000003  | EF       |

| 00000004 | 01       |

| 00000005 | 23       |

| 00000006 | 45       |

| 00000007 | 67       |

| • • •    | • • •    |

| FFFFFFFC | ΕO       |

| FFFFFFD  | E1       |

| FFFFFFE  | E2       |

| FFFFFFFF | E3       |

or as a sequence of words:

| address  | data     |

|----------|----------|

| (in hex) | (in hex) |

| ======   | ======   |

| 00000000 | 89ABCDEF |

| 00000004 | 01234567 |

|          |          |

| FFFFFFC  | E0E1E2E3 |

Both are equivalent and show the same memory contents.

## **Alignment**

A "word-aligned address" is an address that is a multiple 4. The last 2 bits of an aligned address will always be zeros.

Word-sized data and doubleword-sized data must always be stored in word-aligned memory locations. Every instruction is one word (i.e., 4 bytes) long. All instructions must be stored at word-aligned addresses.

Any violation of these alignment requirements will result in an error exception. For example, the load and store instructions will cause an error exception if an attempt is made to move a word to or from an address that is not divisible by 4.

Byte-sized data may be stored at any location in memory; there is no alignment requirement.

This architecture uses only word-alignment; there is no "halfword" or "doubleword" alignment" requirement. Henceforth, whenever we say "alignment", it is understood that we mean "word-alignment".

## **Big Endian**

The BLITZ architecture is "Big Endian", meaning that when a word-sized quantity is stored in 4 bytes of memory, the most significant byte is stored in the first byte (i.e., lowest numbered address) and the least significant byte is stored in the last byte (i.e., the byte with the greatest

address). In other words, if a word is stored at address x, the most significant byte will be stored in byte x and the least significant byte will be stored in address x+3.

Some other (non-BLITZ) computers use "Little Endian" order, in which the least significant byte is stored in the lowest numbered address.

### **Load Store Architecture**

The BLITZ uses a "load-store" architecture. Operations (such as arithmetic and logical functions) can only be performed on data stored in registers. It is necessary to move the data from memory to registers (load it) and back to memory (store it) with separate instructions. The instructions in the following example are not exactly BLITZ instructions, but they give you the idea of load-store architectures. Here, "x", "y", and "z" are the names of some memory locations and "r1", "r2", and "r3" are the names of registers.

```

load x,r1

load y,r2

add r1,r2,r3

store r3,z

```

The first instruction moves data from memory into register "r1". The second instructions moves a number into register "r2". The third instruction adds the values in "r1" and "r2", placing the result into register "r3". The final instruction moves data from register "r3" back to main memory.

BLITZ is a Reduced Instruction Set Computer (RISC) architecture. In a RISC architecture, each instruction is kept very simple, so that instructions may be executed at a fast clock rate. Of course, certain operations are inherently complex, so a couple of instructions may be required in a RISC machine, whereas in another architecture the same operation may require only a single instruction.

Each BLITZ instruction either does a memory access or does a computation. The idea is that each instruction will be executed in one machine (clock) cycle. The goal is to keep each instruction simple so that a faster clock rate can be used, thereby speeding the overall performance of the CPU.

(The BLITZ machine is expected to be emulated in software. When emulated, the RISC architecture may not translate into any increase in speed.)

## **The BLITZ Register Set**

The state of the BLITZ CPU is given by the following registers.

```

User Registers:

===========

r0 - Always zero

r1

r2

. . .

r13

r14 - Frame Pointer

r15 - Stack Pointer

System Registers:

============

r0 - Always zero

r1

r2

. . .

r13

r14 - Frame Pointer

r15 - Stack Pointer

Floating-Point Registers:

_____

f1

f2

f15

Miscellaneous Registers:

_____

PC - Program Counter (32 bits)

PTBR - Page Table Base Register (32 bits)

PTLR - Page Table Length Register (32 bits)

- Status Register (32 bits-see below)

Status Register (32 bits):

31 28 24 20 16 12 8 4 0

0000 0000 0000 0000 0000 0000 00IS PZVN

I = Interrupts Enabled (1=Enabled, 0=Disabled)

S = System Mode (1=System, 0=User)

P = Paging Enabled (1=Enabled, 0=Disabled)

Z = Zero (1=Result was zero)

V = Overflow (1=Overflow occurred)

N = Negative (1=Result was negative)

(All other bits are unused.)

```

## **The Registers**

Each running process can access 16 general purpose registers and 16 floating-point registers.

Each general purpose register contains one word (32 bits) of data. These registers are numbered from 0 to 15 and are named r0, r1, ..., r15. They typically contain signed integer values.

Sometimes the general purpose registers are called the "integer registers" to distinguish them from the floating-point registers.

The floating-point registers each contain two words (64 bits) of data. They are numbered from 0 to 15 and are named f0, f1, ..., f15. Each floating point register contains a double-precision floating point number, stored in the IEEE standard format.

Almost all instructions use at least one of the general purpose integer registers, and some use two or three integer registers. Where ever an integer register is used, any of the 16 registers may be specified. Most integer registers are identical and which register is used is a question for the programmer to determine. However, some registers (in particular, registers r0, r14, and r15) have special uses and functions, as described later.

A subset of instructions (called the "floating-point instructions") access and modify data in the floating-point registers. These instructions all begin with the letter "f". For example there are two addition operations. The integer operation is named "add" and the floating-point operation is named "fadd".

## **User Registers and System Registers**

There are two sets of general purpose registers. Each set has 16 registers. One set is called the "User" register set and the other is called the "System" register set. In each set, the registers are numbered 0 through 15 and named "r0", "r1", ..., "r15".

At any time, the BLITZ processor is executing either in "User Mode" or "System Mode". When the processor is in User Mode, the User Registers are used; when the processor is in System Mode, the System Registers are used.

The use of two sets of integer registers allows kernel traps (for example, "syscall" system calls) to be executed quickly. The user-level process will execute in User mode and will use the User registers. The kernel will execute in System Mode and will use the System registers. During the "syscall" processing, no register saving is necessary; the processor simply changes the Mode to switch to the other register set.

There is only one set of floating-point registers. This set is shared among between User and System processes.

## Register r0

Register r0 is special. Its value is always zero. Any attempt to read from this register will result in zero being returned. Any attempt to store data into this register is perfectly legal; the data will simply be discarded.

## Register r14 - The Frame Pointer

By convention, register r14 is used as a "frame pointer". The frame-pointer register is used in the standard subroutine calling sequence. In conjunction with r15 (the stack pointer), it is used to locate activation records (i.e., "stack frames") in the activation calling stack.

There is no direct architectural support for the frame pointer. In other words, no instruction treats r14 any differently than any other register. In fact, any register could be used with no change to the assembler or machine emulator.

## **Register r15 - The Stack Pointer**

By convention, register r15 points to a stack in memory. This stack is used during procedure calls and returns. This stack is also used during interrupt processing. The "push" and "pop" instructions also use the stack. The push and pop instructions will actually work with any register, but synthetic versions of "push" and "pop" make the use of r15 more convenient. (Synthetic instructions are implemented entirely within the assembler and serve as shorthand for other instructions. They are discussed later.)

By convention, the stack grows downward (toward lower-numbered addresses) from high memory. Register r15 points to the item at the "top" of the stack, i.e., r15 points to the lowest numbered byte that contains stack data. Thus, during a "push" operation, the stack-top register will be decremented before the item is moved to memory, whereas during a pop operation, the data will be moved from memory before the stack-top register is incremented.

Normally, the kernel will maintain its own stack, which will be indexed by the stack-top pointer stored in register r15 in the System Register set. Each user-level process will presumably have its own stack, although this is an operating system issue, not a processor feature. Each user-level process will have a set of User Registers, and its stack-top register r15 will index its stack.

## **Status Register (and Condition Codes)**

The Status Register is defined as a 32 bit register; however, only six of the bits are actually used. When the Status Register is stored as part of the syscall / interrupt processing, the unused bits are set to zero. When the Status Register is loaded during a return from interrupt (the "reti" instruction), the unused bits are ignored.

Three of the status bits (Z=Zero, V=Overflow, and N=Negative) are referred to as the "Condition Codes". These bits are set during certain arithmetic operations to reflect the nature of the computed result. The following instructions modify the condition codes:

add, sub, mul, div, sll, srl, sra, or, and, andn, xor, rem

Note that the following synthetic instructions are shorthand for some of these instructions. Therefore, they also modify the condition codes:

```

mov, cmp, neg, not, clr, btst, bset, bclr, btog

```

Of course the "reti" instruction also modifies the condition codes since it reloads the entire Status Register.

The condition code bits are tested with the various branch instructions, which will conditionally jump according to how these bits are set. Thus, the program can test the result of an operation, such as a "cmp" instruction, and can branch accordingly.

If this bit is set, then interrupts will be processed. If this bit is zero, then interrupts are disabled and incoming interrupts will not be processed; instead they will remain pending until interrupts are once again enabled. At that time, a pending interrupt (if any) will be processed. Only maskable interrupts can be disabled and remain pending. Unmaskable interrupts will always be processed, regardless of the state of this bit, and will never remain pending.

This bit may only be changed by the kernel. That is, this bit may only be changed by privileged instructions, and privileged instructions can only be executed in System Mode.

```

S = System Mode (1=System, 0=User)

```

At any time, the BLITZ processor is executing in either System Mode or in User Mode and this bit determines which mode the processor is in. Presumably the operating system kernel will execute in System Mode and all user-level programs will execute in User Mode. All instructions may be executed when in System Mode. In User Mode, some instructions are forbidden. (The forbidden instructions are called "privileged" instructions.) An attempt to execute a privileged instruction while in User Mode will cause a Privileged Instruction exception and will trap into System Mode.

This bit may only be changed by the kernel. That is, it may only be changed by privileged instructions, which may only be executed in System Mode.

```

P = Paging Enabled (1=Enabled, 0=Disabled)

```

The BLITZ architecture provides support for virtual memory via a page table with automatic address translation. If this bit is set, then address translation will occur whenever the program accesses main memory. Whenever an instruction accesses memory, the address it provides will be interpreted as a "logical" address (also called a "virtual" address). This logical address will be translated into a physical address by the CPU's translation hardware before being used. The physical address will then be used to determine which bytes in memory are examined or modified by the instruction. If this bit is zero, then every memory address generated by an instruction will be used as is, with no translation. Presumably, an operating system kernel will run with paging disabled and user-level programs will run with paging enabled.

This bit may only be changed by the kernel. That is, it may only be changed by privileged instructions, which may only be executed in System Mode.

```

Z = Zero (1=Result was zero)

```

If the result of the arithmetic operation is zero (i.e., all bits are zero), then this bit will be set to 1. Otherwise, it will be cleared to zero.

If the execution of the arithmetic operation caused overflow, then this bit will be set to 1. Otherwise, it will be cleared to zero. Overflow may occur for add, sub, mul, div, rem, and fcmp.

```

N = Negative (1=Result was negative)

```

If the result of the arithmetic operation is negative (i.e., the most significant bit is "1"), then this bit will be set. Otherwise, it will be cleared to zero.

## The Program Counter (PC) Register

There is a 32-bit register called the "PC", which contains the address of the next instruction to execute. It is modified with instructions that branch or transfer the flow of control.

## The Page Table Base Register (PTBR) Register

The Page Table Base Register ("PTBR") contains the address of the page table. The page table is stored in main memory and this register will always contain a word-aligned address. This register is used whenever the page table is consulted by the CPU's address translation hardware. In particular, when a virtual address is translated into a physical address, this register will be used to locate the page table in main memory. This only happens when paging is enabled by the "Paging Enabled" bit in the Status Register. If paging is disabled, this register is ignored. This register will contain a physical address, not a virtual address.

This register can only be loaded with the "ldptbr" instruction, and it cannot be examined directly.

## The Page Table Length Register (PTLR) Register

The Page Table Length Register ("PTLR") is used in conjunction with the Page Table Base Register. The page table consists of a number of entries, stored sequentially in memory. Each entry is 4 bytes (one word) long. This register contains the number of bytes in the table and therefore it will always be a multiple of 4.

This register can only be loaded with the "ldptlr" instruction, and it cannot be examined directly.

## **Instruction Formats**

Every BLITZ instruction is 4 bytes long. The first byte of the instruction is the op-code, indicating what the instruction is. The remaining 3 bytes are interpreted differently. Some instructions have no operands, in which case the remaining 3 bytes are ignored. Other

instructions take several operands, in which case the operands are encoded into the remaining 3 bytes. There are seven different instruction formats, named Format A, Format B, ..., Format G.

Here are the instruction formats. Each line shows how the 32 bits of an instruction are to be interpreted.

```

Format A:

XXXX XXXX

----

----

Format B:

XXXX XXXX CCCC ----

Format C:

XXXX XXXX

cccc aaaa

Format D:

xxxx xxxx cccc aaaa

bbbb ----

Format E:

xxxx xxxx cccc aaaa vvvv vvvv

vvvv vvvv

Format F:

xxxx xxxx rrrr rrrr rrrr rrrr rrrr

Format G:

XXXX XXXX CCCC ---- VVVV VVVV VVVV

```

The various fields in the instructions are given by the following legend:

```

xxxx xxxx Op code (8 bits)

aaaa Register A (4 bits)

bbbb Register B (4 bits)

cccc Register C (4 bits)

vvvv vvvv vvvv vvvv vvvv Immediate value (16-bits, sign-extended)

rrrr rrrr ... rrrr Relative displacement (24-bits, sign-extended)

(These bits are ignored)

```

There are 16 general purpose registers and they are encoded in the obvious way in 4-bit fields (shown above as "aaaa", "bbbb", and "cccc") in the instructions:

```

0000 - Register r0

0001 - Register r1

0010 - Register r2

...

1111 - Register r15

```

Many instructions take one or more general purpose registers as operands. These are referred to as Register A, Register B, and Register C. For example, the general format of the multiply instruction is:

```

mul regA,regB,regC

```

A specific instance of this instruction might be:

```

mul r7,r8,r13 ! Multiply r7 by r8 and place result in r13.

```

In this instruction we have:

```

aaaa = RegA = r7 = 0111

bbbb = RegB = r8 = 1000

cccc = RegC = r13 = 1101

```

The op code for the "mul" instruction (Format D) is 98 (in binary: 0110 0010). Thus, this instruction would be encoded as:

Some instructions operate on the floating-point registers instead of the general purpose registers. An example is the floating-point multiply instruction:

```

fmul freqA,freqB,freqC

```

A specific instance of this instruction might be:

```

fmul f3,f4,f9 ! Multiply f3 by f4 and place result in f9.

```

There are 16 floating-point registers and (like the general purpose registers) they are encoded in the obvious way in 4-bit fields (shown above as "aaaa", "bbbb", and "cccc") in the instructions:

```

0000 - Register f0

0001 - Register f1

0010 - Register f2

...

1111 - Register f15

```

The floating-point instructions (like "fmul") interpret the 4-bit register fields (aaaa, bbbb, and cccc) as indicating floating-point registers; all other instructions interpret the 4-bit fields as meaning general purpose registers. Thus, the bit pattern

```

0101

```

may mean either "r5" or "f5", depending on which instruction it is used in.

The op-codes are assigned in such a way that the first 3 bits of the op-code indicate the format of the instruction.

|         | op-code                                                                     |

|---------|-----------------------------------------------------------------------------|

| range   | in binary                                                                   |

| ======  | =======                                                                     |

| 0-31    | 000                                                                         |

| 32-63   | 001                                                                         |

| 64-95   | 010                                                                         |

| 96-127  | 011                                                                         |

| 128-159 | 100                                                                         |

| 160-191 | 101                                                                         |

| 192-223 | 110                                                                         |

| 224-255 | 111                                                                         |

|         | ======<br>0-31<br>32-63<br>64-95<br>96-127<br>128-159<br>160-191<br>192-223 |

## 16-Bit Sign-Extended Immediate Values

Many of the instructions allow for an immediate (or "literal") value to be included directly in the instruction. (In particular, all Format E and Format G instructions allow it.) For example, the subtract instruction may include a value directly:

```

sub r3,27,r4

```

This instruction subtracts 27 from the value stored in register r3 and stores the result in r4. The data (27) is specified immediately; it is not stored in a register. Instructions such as these include a 16 bit field in the instruction to contain the value. When executed, the 16 bits are interpreted as a signed integer. Thus, the 16 bit value is "sign-extended". In other words, the most significant bit (bit 15) is duplicated to fill the value out to 32 bits. This means that any value between - 32768 and 32767 can be specified literally. If you wish to subtract a number outside this range, you can not use a literal value; you will have to first place the value in a register of its own. (For example, you might use the "set" instruction to accomplish this.)

Note that the logical operations (such as shift left logical "sll" and exclusive-or "xor") can also take 16-bit immediate values. These values are also treated as signed integers and are signed-extended to 32 bits before being used. Any attempt to use an out-of-range number, as in the following example, will be caught by the assembler and flagged as an error.

```

xor r3,0xAB12CD34,r4 ERROR!

```

The programmer must be careful in situations like the following. Presumably the programmer is trying to flip a single bit (bit 15).

```

xor r3,0x8000,r4

```

The assembler will not flag this as an error and will produce the same code as for this instruction:

```

xor r3,0xFFFF8000,r4

```

One exception to the sign-extension rule is for the "sethi" and "setlo" instructions. These instructions are Format G instructions, so they contain a 16-bit immediate value. However, in these instructions, the value is not sign-extended before use.

## **24-Bit Relative Displacements**

Format F instructions are concerned with branching and jumping. The following instructions have Format F version: the "call" instruction, the "jmp" instruction, and the conditional branch instructions (such as "bne", "bl", and "bge").

Format F instructions contain a 24-bit field, which gives a displacement (also called an "offset"). This displacement is relative to the current location. More precisely, the 24-bit offset is sign-extended to 32-bits. This is then added to the address of the instruction (not the address following the instruction, as in some architectures) to give the target address. The target address is the address to be jumped to. If the branch is taken, the next instruction to be executed will be the instruction stored at the target address.

In the BLITZ architecture, logical (i.e., virtual) address spaces are limited to 16M bytes. (Recall that any byte in a 16M byte address space can be addressed with 24 bits.) Therefore, any byte in

the logical address space may be addressed using a 24-bit relative displacement in a Format F instruction located anywhere in that address space. The address computation (adding the current address to the 24-bit displacement) is done using 32-bit arithmetic, but any bits beyond 24 are simply ignored when paging is enabled.

The benefit of using relative displacements instead of absolute addresses is that the code can be relocated (i.e., moved) from one area of memory to another, without having to be modified. As long as the relative separation of the Format F (branch) instruction and the target instruction of the branch remains unchanged, no modification of the branch instruction is necessary.

Consider the following code, for example:

The branch instruction will contain a displacement of -12, meaning that the target instruction is 12 bytes before the branch instruction. At runtime, this code may be loaded at any address. For example, it might be loaded at addresses starting at 0x65432100:

| 6543 | 2100 | loop: | add | r5,5,r5 |

|------|------|-------|-----|---------|

| 6543 | 2104 |       | add | r3,1,r3 |

| 6543 | 2108 |       | cmp | r3,17   |

| 6543 | 210C |       | ble | loop    |

When the processor executes the branch instruction, it takes the current value of the program counter (6543210C) and adds the relative offset in the instruction (i.e., -12), giving the address of the instruction labeled "loop". Obviously, if this code had been loaded at some other address at run-time, it would still work correctly.

To be precise, the 24 bit displacement is signed extended to 32 bits. Then this value is added to the address of the branch instruction. This means that the target of a branch instruction must lie within –8,388,608 to 8,388,607 bytes of the branch instruction. If the machine is operating with paging enabled, then the target address is a virtual address. It will be truncated to 24 bits before being translated into a 32-bit physical address.

(Since the branch instruction must be at an aligned address and since the target address must be aligned, the displacement in a branch instruction should also be divisible by 4. Therefore, the last 2 bits of any 24-bit displacement in a Format F instruction should be zero; if the displacement is not divisible by 4, an Alignment Exception will occur.)

## **Addressing Memory**

In order to fetch or store data to / from memory, the address must first be placed in a register. The "set" instruction is ideal for moving the address into a register. For example, the following code first moves the address of "myVar" into register r1. Then it uses that register to fetch from memory. This code increments the word whose address is "myVar".

```

set myVar,rl ! Move address of myVar into r1

load [r1],r2 ! Move data from myVar into r2

add r2,1,r2 ! Increment r2

store r2,[r1] ! Store data back, using same address

```

A second addressing mode allows an integer offset to be added to a register to compute the effective address. For example, assume "myArr" is the address of the first element of an array of words. We wish to increment the sixth element of this array. We will need an offset of 20, since each element is 4 bytes long.

```

set     myArr,r1

load     [r1+20],r2

add     r2,1,r2

store     r2,[r1+20]

```

A third addressing mode allows us to add the contents of two registers together to compute the effective address. For example, if the offset into the array has been computed and placed in register r3, then we can use the following code to access the desired element.

```

set     myArr,r1

load     [r1+r3],r2

add     r2,1,r2

store     r2,[r1+r3]

```

A common thing to do is to access fields in the activation record (or "frame"). Assume that variable x is a local variable stored at offset -12 in the frame. Then the following code would be used to increment x.

In this example, we assume that the "standard subroutine calling conventions" have been followed and that "r14" points into the frame stored on the top of the stack. In the standard calling conventions, which are described elsewhere, the frame pointer will point into the middle of the frame, not to the lowest byte in the frame. The local variables will actually be stored in the frame at negative offsets from the frame pointer.

## **Synthetic Instructions**

There are several "synthetic" instructions. Technically, these are not true BLITZ instructions. Instead, they are introduced to make life easier for the programmer. Whenever the assembler sees a "synthetic" instruction, it will translate it into one or two legal BLITZ instructions and will use those instructions instead.

For example, "set" is a synthetic instruction. It will be expanded into two instructions. Consider the following code:

```

set myArr,r1

load [r1],r2

```

The "set" instruction will be automatically expanded by the assembler into two instructions, giving:

```

sethi hi(myArr),r1

setlo lo(myArr),r1

load [r1],r2

```

Here we are using "lo" and "hi" to indicate the lo-order and hi-order 16 bits of the full 32-bit value given by the symbol "myArr", although these are not really part of the assembler syntax.

The "sethi" and "setlo" instructions are discussed later, but in short, "sethi" moves 16 bits of data into the register, and the "setlo" instruction brings in the remaining 16 bits of data.

You might consider the following code sequence, which would be more efficient. However, this code sequence is subject to a very subtle bug.

```

sethi hi(myArr),r1 ! Warning: This code sequence load [r1+lo(myArr)],r2 ! may not do what you expect.

```

Recall that the 16-bit immediate value "lo(myArr)" in the load instruction would be sign-extended. The above instruction sequence will work only if the most significant bit of "lo(myArr)" was zero; otherwise it would be sign-extended, causing the address computation to result in a very different address. Since code may be relocated during linking, it is difficult to know whether this condition would be met. Therefore, the "setlo" instruction should always be used when moving 32-bit constant values.

### **Assembler Comments**

The exclamation point (!) is used to begin comments. The comment runs through the end-of-line. As a point of style, every line of assembler code should probably be commented.

When a single comment applies to several instructions, I prefer to use a period as demonstrated below to indicate that a multi-line comment applies to several instructions.

```

set     myVal,r1    ! Increment myVal

load     [r1],r2     ! . by one

add     r2,1,r2     ! .

store     r2,[r1]     ! .

cmp     r2,47     ! If myVal >= 47

bge     loop     ! . then goto loop

```

## **Labels and White Space**

Each instruction may be preceded by an optional label. This label may then be the target of a "branch" or "call" instruction. Data locations in memory may also be labeled, in which case the label could be used in "load" or "store" instructions.

If a label is present, it must be at the beginning of the line and must be followed by a colon. The instruction op-code is separated from the label by some white-space (usually a single tab character). The instruction op-code is followed by white space (usually a tab or two) and the operands. These can optionally be followed by some white space and a comment.

A label may also appear on a line by itself, in which case it applies to the current location counter, and will therefore be set to the address of the next instruction (notwithstanding things like ".align" pseudo-ops that may change the location counter). Op-codes (both legal BLITZ instructions and pseudo-ops) must be preceded by white space, typically a tab or two.

The convention is to try to make things line up neatly. For example:

```

myLoop:

! myLoop:

.,val,r1

[r1],r2

r2,1,r2

r2,[r1]

set

! Increment myVal

load

. by one

add

r2,[r1]

store

!

r2,47

myLoop

! If myVal >= 47

cmp

! . then goto myLoop

bge

myVal:

! myVal: counter of things

.word

```

## **The Program Counter**

Every computer processor contains a register called the Program Counter (or "PC") which contains the address of the next instruction to be executed. In the simplest model of computer operation, the processor repeatedly executes this algorithm:

Sometimes the instruction will modify the flow of control (a "call" or "branch" instruction). For such instructions, a "result" will be stored into the PC register, causing the next instruction to be fetched from a new address.

In the BLITZ processor, each instruction executes to completion before the next instruction begins. There is no pipelining of instructions. (Not included in this discussion is the processing of exceptions, asynchronous interrupts, or "syscall" traps. When such interrupts occur, the above processing loop is more complex.)

### **The Location Counter**

As the assembler scans and processes each line of code, it keeps track of the current memory location into which each instruction will be placed. To do this, the assembler keeps a variable called the "Location Counter", which should not be confused with the "Program Counter". The location counter and the program counter are different.

It is important to understand that the location counter is an assembly-time concept; it does not exist at run time. On the other hand, the program counter is a run-time register (named "PC") and only has a value when the program is running. When the assembler encounters a branch instruction, it never "takes" the branch; instead it simply moves on to the next instruction in the source file by incrementing the location counter. Later, at runtime, when the CPU encounters a branch instruction, it may take the branch by modifying the PC.

Every time the assembler encounters an instruction, the location counter is advanced by 4 (i.e., by the size of the instruction). Even when a branch instruction is processed, the location counter

is always advanced by 4 and the instruction on the line following the branch is then processed. To repeat, a branch is never "taken" by the assembler.

When the assembler encounters a label, it adds a new definition to its symbol table, using the current value of the location counter as the definition of the symbol. When the assembler encounters a branch instruction or a load or store instruction using some label, it looks that label up in the symbol table. It will use the value of that symbol in assembling the branch instruction.

Assemblers make two passes over the source program. In the first pass, the location counter is set to zero, and the source code file is scanned line-by-line. Each time an instruction is encountered, the location counter is advanced by the length of the instruction, but no code is generated in the first pass. Whenever a label is encountered, it is entered into the symbol table, using the current value of the location counter as the symbol's definition.

In the second pass, the location counter is reset to zero. Then, the source code is examined again line-by-line from beginning to end. This time, machine code is generated and written to the output as each instruction is scanned.

This two-pass approach allows branches and other instructions to use labels that are defined either before or after the instruction. As the second pass begins, all symbols are already defined. As the second pass proceeds, the machine code for each instruction can be determined by plugging in the symbols' values as necessary.

Branch and call instructions in the BLITZ architecture are "relative", and not "absolute". Each branch and call instruction contains a 24 bit field to specify the target address to be jumped to. This 24 bit field does not contain the absolute address of the target instruction. Instead, this field is interpreted as a signed number, which will be added to the current program counter at run-time to give the target address. Although the assembler does not know where the program will ultimately be loaded in memory, it is able to compute the relative distance between a branch instruction and its target address. Thus, it can produce code containing the correct relative displacement.

The assembler can be used to place data and instructions into different segments. The three segments are named ".text", ".data", and ".bss". The assembler maintains a distinct location counter for each segment. Thus, there is a ".data" location counter, a ".text" location counter, and a ".bss" location counter. At any one time, the assembler is "in" only one segment, as determined by the .data, .text, and .bss pseudo-ops. For example, if the last pseudo-op was .text, all generated data following it will be placed in the ".text" segment and the corresponding location counter will be incremented.

## <u>Pseudo-Ops (Assembler Directives)</u>

The following sections describe several "pseudo-operations", which control and direct the assembler in its task. Pseudo-ops are sometimes called "assembler directives".

Pseudo-ops are included in the assembly language program file, mixed in among the real BLITZ instructions. However, pseudo-ops are not executed at runtime; instead they tell the assembler how to assemble other instructions and what to put into memory before program execution begins. For example, a pseudo-op could be used to initialize a variable with some particular value. The value can be coded using convenient (C-like) notation, freeing the programmer from having to specify the precise bit-pattern used to represent the value.

Pseudo-ops begin with a period to make it easy to distinguish them from BLITZ instructions.

### **Character Data**

Here are examples of the ".ascii" pseudo-op:

```

.ascii "abc"

.ascii "BLITZ programming is fun!\n"

```

The ".ascii" pseudo-op places N bytes of data in memory, where N is the number of bytes in the character string. A number of escapes (such as "\n") can be used to place non-printable ASCII codes in string.

The standard "C" string convention is to terminate every string of characters with the NULL character. Note that the .ascii pseudo-op does not place a terminating NULL character in the string. If this is what you want, you must include it explicitly. For example:

```

.ascii "Hello, world.\n\0"

```

### Data

```

.byte expression

.word expression

```

These pseudo-ops place data values in memory. In each case, arbitrary expressions may be provided, as long as they can be fully evaluated at assembly-time. These expressions may include many of the operators (such as + and \*) available in the C language.

## **Double Constants**

```

.double value

```

This pseudo-op places an 8 byte (64 bit) double precision floating-point value in memory. Here are some examples, showing the ways in which the value may be specified.

## **Alignment**

The ".align" pseudo-op will force the location counter to be word aligned. In other words, one or more bytes of padding may be inserted to round the location counter up to an address divisible by 4.

```

.align

```

In the first line of the following example, up to 3 bytes will be inserted (if necessary) to bring the location counter up to a multiple of 4. In the second line, 6 bytes will be allocated. In the next line, 2 additional bytes will by allocated so the next word will be placed in an aligned address.

```

.align

.ascii "abcdef"

.align

.word 43

.word "cs30"

.word -1

.word 0x0123abcd

```

If the location counter is already aligned, this pseudo-op will insert no padding bytes. Thus, it never hurts to place an align pseudo-op directly before instructions that require a particular alignment, and it is necessary if the preceding instructions may have left the alignment wrong.

## **Uninitialized Data Space**

```

.skip N

```

This pseudo-op skips over N bytes, where N is any expression. The assembler and linker will fill these bytes with zeros.

## **Segment Control**

A running process is loaded into main memory before execution begins. In Unix, a running process is divided into four "segments". These segments have the following names:

.data

.text

.bss

.stack

Before a program begins execution, initial data will be loaded into the ".data", ".text", and ".bss" segments. The assembler is used to specify exactly what will be loaded into the ".data", ".text", and ".bss" segments and how long they will be. For example, the ".data" segment might be loaded with 100 bytes giving the initial values of several variables. The ".text" segment might be loaded with 11,000 bytes of machine instructions. Often the ".bss" segment is not used and will have a length of 0 bytes.

After loading, the OS will usually mark the bytes in the ".data" segment read/write, and the bytes in the ".text" segment will be marked "read-only". Any attempt at run-time to modify a byte in the ".text" segment will result in an exception and the user-level program will be aborted by the OS. Any attempt to access a byte outside of any segment will also result in a similar error.

The ".stack" segment will be marked read/write, and has no fixed size; instead any attempt to access bytes beyond the end of the ".stack" segment will result in new pages being added to that segment.

There are three pseudo-ops that allow control over which segment to place data and instructions into. They are:

- .data

- .text

- .bss

These pseudo-ops determine into which segment the following instructions and/or data will be placed. Each "remains in effect" until a new .data or .text or .bss pseudo-op is encountered.

The .bss segment contains data that will be initialized to zero. Thus, no space will actually be consumed in the executable "a.out" file; the file will merely contain information about which bytes of the virtual address space must be initialized to zero before execution begins. As a consequence, the .bss segment may contain only .align and .skip pseudo-ops. Instructions and other pseudo-ops are not allowed in the .bss segment.

At assembly time, each of the three segments is assumed to start at location zero. Later, when the program is loaded into main memory, an address will be selected. Also, the size of the segment is rounded up to the nearest page boundary. In a machine with 8K byte pages, our ".data" segment with 100 bytes would be rounded up to 8K bytes. The ".text" segment, with 11,000 bytes would be rounded up to 16K bytes. Then an address is selected for each of the four segments and the initial data is loaded into the appropriate memory locations.

## **Symbols**

Symbols may be defined in several ways. The most common way is when an instruction is labeled. Another way is when the location of data in memory is allocated (e.g., with a ".word" pseudo-op) and a label is present.

When the assembler encounters a label, it makes a new entry in its symbol table, associating the symbol with the current value of the location counter. It also makes a note in its symbol table of which segment this address is in. Later, when the several separately-assembled pieces of the program are linked together, each segment will be assigned a specific address. This will require the value of the symbol to be adjusted. Furthermore, every instruction that uses the symbol must be modified to reflect the fact that the symbol is being adjusted. Obviously, there is a lot of information in the ".o" files that indicates which symbols are used as well as where and how they are used, so that the linker can make these adjustments when the various segments are put together.

Symbols may also be defined directly using the "=" pseudo-op. Here is an example:

Note that "=" is a pseudo-op (like ".align" or ".text") although "=" differs in that it is not given an alphabetic name beginning with a period.

In this example, we have introduced a symbol called "incrAmt" and set its value to 3. Such a symbol is an assembly-time constant: it can never change. This symbol is absolute, which means it is not relative to any segment. During linking, when the segments are assigned addresses, no

adjustment will be needed to the "add" instruction. The value of 3 will be used. The symbol "incrAmt" may be used any place the constant 3 may be used.

In this example, the operand of the "=" pseudo-op is "3". In general, the operand can be any expression, as long as it can be evaluated at assembly-time.

## **External Symbols**

```

.export localSymbol

.import foreignSymbol

```

It is assumed that "localSymbol" is defined within the ".s" source file that contains the .export pseudo-op. It is assumed that "foreignSymbol" is not defined in the file containing the ".import" pseudo-op but is defined in some other file that is assembled at some other time and linked with this file. The assembler and linker will check that .export and .import are used correctly.

When the assembler processes a ".s" source file and produces a ".o" object file, it will include information in the ".o" file to identify the symbols used and give information about their values (or about their locations, if they are labels). The .export pseudo-op will make "localSymbol" visible to other ".o" files with which this file is linked. The .import pseudo-op will make a symbol called "foreignSymbol" defined in some other file visible and usable within the current file.

Consider this example:

```

.export main

.import printf

...

main: add r1,234,r3

...

call printf

...

```

When an imported symbol (such as "printf" in this example) is used in this file, the linker will look for a definition of it in other ".o" files and will modify instructions (such as the "call" instruction) in the executable file to point to it. In this example, a routine called "main" is defined and exported. Thus, this routine can be called from other ".s" files which are assembled separately.

It is a good idea to put an ".align" pseudo-op before the first instruction, in case a previous data item left the location counter on a non-word aligned boundary.

Note that the following is in error since the symbol "main" would be set to point to the "padding" bytes inserted by the ".align".

```

main:

.align

add r1,234,r3

```

## **Interrupt Processing**

In this document, we use the term "interrupt" very generally to refer to an interruption in the normal sequential execution of instructions. We use the terms "exception" and "trap" more specifically, as discussed next.

Asynchronous interrupts may occur at anytime. These are triggered by events outside of the instruction processing sequence of the CPU. For example, a hardware device (such as a disk or the interval timer) may suddenly require attention. The device will send an electrical signal to the processor, which will trigger interrupt processing. This sort of interrupt is referred to as an "asynchronous interrupt" or a "hardware interrupt".

Synchronous interrupts occur as a result of executing instructions within the CPU. These can be divided into two categories: those that are the result of problems and those that are specifically intended. Interrupts that are the result of problems arising during instruction execution are called "exceptions". Examples include "Illegal Instruction" and "Alignment Exception". In the case of an exception, some unexpected event occurred during the execution of an instruction.

The only intentional interrupt is caused by the system call instruction ("syscall"). This sort of an interrupt is often referred to as a "trap", rather than as an "exception". It is used by a user-level program to enter (or invoke) the kernel of the operating system.

This table summarizes our terminology and lists all types of interrupts:

```

Interrupt:

Asynchronous Interrupts (Hardware):

- PowerOnReset

- TimerInterrupt

- DiskInterrupt

- SerialInterrupt

- HardwareFault

Synchronous Interrupts:

Exceptions:

- IllegalInstruction

- Arithmetic

- Address

- PageInvalid

- PageReadOnly

- PrivilegedInstruction

- Alignment

- ExceptionDuringInterrupt

Trap:

- Syscall

```

When an interrupt occurs and is serviced, the following actions occur. (If the interrupt is not serviced, it remains pending, as discussed later, and will be serviced at some other time.)

First, the currently executing instruction is finished. In the case of an asynchronous (hardware) interrupt, the current instruction runs to completion and the PC is left pointing at the next instruction. In the case of an exception, the instruction execution is preempted and the PC is left pointing to the offending instruction. Furthermore, in the case of an exception, the offending instruction has no effect; the state of the CPU and memory is not altered. It is as if the instruction had never been attempted. In the case of a "syscall" trap, the PC is left pointing to the instruction following the "syscall".

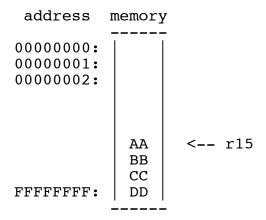

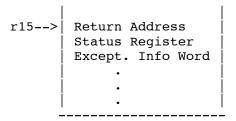

Second, an "exception info word" is pushed onto the stack. In the case of a PageInvalid or PageReadOnly exception, the offending virtual memory address will be pushed onto the system stack. In the case of a "syscall" trap, the "system trap number" will be pushed onto the system stack. By pushed onto the system stack, we mean that System Register "r15" (not User Register r15) will be used. For all other interrupt types, the "exception info word" will be all zeros.

Third, the Status Register will be pushed onto the system stack.

Fourth, the PC will be pushed onto the system stack. At this point, the system stack looks like this:

Fifth, the following bits of the Status Register will be changed. This will change the CPU to System Mode, disable subsequent interrupts, and disable address translation via the page table.

I := 0 S := 1 P := 0

Sixth, the PC will be loaded with the address of one of the Interrupt Vector entries. This has the effect of causing a branch to the appropriate interrupt handler code. The interrupt vector consists of several words stored in low memory, as shown below. In particular, there is one word for each type of interrupt. The table below gives the addresses of the table entries (in hex). (Normally, the OS would have stored into each word of this table a "jump" instruction, which will branch to the first instruction of the interrupt handler for that type of interrupt.) In this step, the PC is simply loaded with the corresponding address from the following table.

Interrupt Vector in Low Memory

| Address | Description                             | Maskable |

|---------|-----------------------------------------|----------|

| ======  | ======================================= | =======  |

| 000000  | Power On Reset                          | No       |

| 000004  | Timer Interrupt                         | Yes      |

| 800000  | Disk Interrupt                          | Yes      |

| 00000C  | Serial Interrupt                        | Yes      |

| 000010  | Hardware Fault                          | No       |

| 000014  | Illegal Instruction                     | No       |

| 000018  | Arithmetic Exception                    | Yes      |

| 00001C  | Address Exception                       | No       |

| 000020  | Page Invalid Exception                  | No       |

| 000024  | Page Readonly Exception                 | No       |

| 000028  | Privileged Instruction                  | No       |

| 00002C  | Alignment Exception                     | No       |

| 000030  | Exception During Interrupt              | No       |

| 000034  | Syscall Trap                            | Yes      |

To repeat what happens, given the type of the interrupt, the corresponding address (from the above table) is moved into the PC. This will cause a transfer of control directly into the table. Normally, each table entry will hold a "jump" instruction; if so, this jump instruction will be executed on the following instruction cycle, causing a second transfer of control to the correct interrupt handler routine.

Some interrupts can be handled simply by the interrupt handler routine and a return to the interrupted process can be made fairly quickly. (For example, a Serial Interrupt may indicate that the user has pressed a character key on the keyboard. It may be adequate to simply query the device and save the character in some sort of a buffer before returning to the interrupted process. The details are operating system dependent.)

The Return From Interrupt instruction (the "reti" instruction) would normally be used to return from an interrupt handler routine to the interrupted process. The "reti" instruction works as follows. First, the "reti" instruction will restore the PC by popping the top value from the from system stack and moving it into the PC, thereby preparing a return in the flow-of-control back to the interrupted process. Then, "reti" will restore the Status Register, by popping the next value from the from system stack into the Status Register. Then, "reti" will pop and discard the next value (the exception info word) from the system stack. After "reti" has completed, instruction execution will then resume in the interrupted process.

Generally, the interrupted process will be a user-level process and so will have been executing in User Mode, although sometimes interrupts will occur while the kernel itself is executing. If a User Mode process was interrupted, none of its registers will have been modified while the handler routine serviced the interrupt, since the interrupt handler executed in System Mode. If the handler routine was written correctly, the interrupted process will be entirely unaffected and unaware that it was interrupted.

For example, if the interrupt was a PageInvalid or PageReadOnly exception, then presumably the necessary page will have been moved into a memory frame during the execution of the interrupt handler. The PC will have been left pointing to the instruction that caused the exception. Upon return, the interrupted instruction will be re-tried and will succeed this time (unless another different interrupt occurs first).

## **Masking Interrupts**

Some interrupt types are said to be "maskable" and the rest are "unmaskable". When an unmaskable interrupt occurs, it will be serviced as soon as possible, namely on the next instruction cycle. Maskable interrupts may be serviced either immediately or at some later time, when the software is ready to deal with the interrupt. (By "serviced", we mean that the interrupt processing sequence discussed above will be performed. Three words will be pushed onto the system stack and a branch will be made to the interrupt handling routine.)

The Interrupt Enabled bit (the "I" bit) in the Status Register determines whether a maskable interrupt will be serviced when it occurs. If the "I" bit is set to one, then the interrupt will be serviced immediately, without delay (i.e., within the current or next instruction cycle) and a transfer will be made to the handler routine.

If the interrupt type is unmaskable, then interrupt processing will occur regardless of the state of the "I" bit. The interrupt cannot be masked or disabled. If the interrupt is signaled, the interrupt sequence will occur and a transfer will be made to the corresponding handler.

If the interrupt type is maskable, and the "I" was previously cleared to zero, then the interrupt servicing sequence will not occur. No transfer to the handler routine will be made and instruction execution will continue without interruption. Furthermore, the interrupt will remain "pending". That is, the moment that interrupts are re-enabled (by setting the "I" bit to one), the interrupt servicing sequence will be initiated and a transfer to the interrupt handler will occur.

There may be several interrupts pending, but within a single interrupt type, there will be at most one pending interrupt. For example, there could be a Disk Interrupt and a Timer Interrupt both pending, but there can be at most one Disk Interrupt pending. Of course the disk device may repeatedly request a Disk Interrupt after the first has been fully serviced (and the "I" has been reset to one, re-enabling interrupts) causing the handler to be invoked a second time.

## **Exception During Interrupt**

During interrupt servicing, data is pushed onto the system stack. If system register "r15" is not aligned properly or points to an invalid address, there are going to be problems. In other words, an "Address Exception" or an "Alignment Exception" can occur during the processing of interrupts.

(Note that an exception may occur during the servicing of an exception. To be precise and avoid infinite regress, we should probably avoid saying that "an exception occurs during the servicing of an exception" and just talk about what happens.)

What happens when we have problems while servicing an interrupt? The current interrupt is abandoned and the PC is loaded with the address of the ExceptionDuringInterrupt entry in the low-memory interrupt vector. While processing the original interrupt, the processor may have successfully pushed one or two words onto the system stack before encountering a problem. In any event, no further attempt to push words onto the stack is made. Instead, the branch is immediately made to the ExceptionDuringInterrupt handler.

Presumably, an ExceptionDuringInterrupt indicates a catastrophic software failure of the operating system itself and will be handled by printing a final message before terminating the operating system.

## **Virtual Memory Address Translation and The Page Table**

The Paging Enabled bit in the Status Register (the "P" bit) tells whether virtual memory address translation is turned on or not. If the "P" bit is cleared to zero, then there is no address translation. Every address generated during instruction execution is used "as is" as an index into physical memory. By "physical memory", we mean the main memory of the processor.

Physical addresses are a full 32 bits. If a physical address is beyond the end of the installed memory, then an Address Exception occurs and interrupt servicing begins (as discussed later). A 32 bit address allows up to 4G bytes to be installed and addressed, although since I/O devices are memory-mapped, several addresses will be unavailable for use. The Interrupt vector lies in low memory and memory-mapped I/O devices will be mapped into the highest addresses in the physical address space.

The BLITZ processor includes a Memory Management Unit (MMU), which is either enabled or disabled, as determined by the "P" bit. When enabled, the MMU provides a simple page-table

based translation scheme, which may be used by an operating system to implement virtual memory.

As a program is running and instructions are being executed one after another, "logical" addresses are generated. Every instruction must be fetched from memory, so the execution of each instruction always begins by fetching a 32-bit word from memory. The current value of the PC is used as the logical address of the word to fetch. Many instructions will not access memory again; all of their action will be done using CPU registers only. However, several instructions (such as "load" and "store") will go to memory a second time. The "load" instruction will fetch from memory and the "store" will write data to memory. One instruction, the "test and set" ("tset") instruction, will go to memory two more times. The tset instruction will fetch a word and then will store data to that same word. Regardless of which instruction is being executed, the CPU will generate a stream of "logical" addresses that will be used to fetch and store data from/to memory. Logical addresses are 32-bits long.

When address translation is disabled, the "logical" addresses will be used as "physical" addresses directly. There will be no translation: the address will be used as is.

When address translation is enabled, the logical address will be broken into three fields, denoted "xxx", "ppp", and "ooo" below. The full 32-bit logical address is shown below, with the bits numbered.

```

31 28 24

0

20 16

12

8

==== ====

==== ====

==== ====

xxxx xxxx pppp pppp

pppo 0000 0000 0000

- high order bits (8 bits)

XXXXXXX

ppppppppppp - page number (11 bits)

ooooooooooo - offset (13 bits)

Page Size = 8K bytes

Page Table Entry = 4 bytes (32-bits)

Max Page Table Size = 2K entries = 8K bytes

```

The high-order 8 bits of a logical address ("xxx") are ignored and zeros are used. This limits the amount of addressable memory to 16M bytes, i.e., the amount that can be addressed with only 24 bits of address. This limits each logical address space to 16M bytes. Since the upper bits are ignored, it is not an error to address bytes outside the 16M byte limit; instead wrap-around occurs with no fanfare. Note that with a 24-bit offset (as is provided in all Format F instructions), every byte within the logical address space can be addressed.

The logical address space is broken into "pages" and each page is 8K bytes long. Since the logical address space is 16M bytes long, there are 2K (i.e., 2048) pages in each logical address space. The "ppp" field is 11 bits long and is used to select the page. Since each page is 8K bytes long, 13 bits are needed to select the individual byte within the page. This is given by the "ooo" (offset) field in the logical address.

Physical memory is divided into "frames" and each frame is 8K bytes long. Frames always begin on even (8K) boundaries. Each frame can hold exactly one page, but there need not be a simple one-to-one mapping between the pages in a logical address space and the frames in physical memory. (In a simple one-to-one mapping, frame 0 holds page 0, frame 1 holds page 1, frame 2 holds page 2, and so on.) The page table allows the mapping to be more complex.

A page table is an array of "page table entries". Each page table entry is one word (32 bits) long. A page table may have up to 2K entries, but it may have fewer (possibly zero) entries as well. (Note that a page table of the maximum size will exactly fit into a single page/frame.)

A page table is stored in memory, not in special MMU registers. In fact, the MMU has no visible state or registers of its own, beyond the "Page Table Base Register" and the "Page Table Length Register". At any one time, there is a current page table and this is given by the contents of these two registers. If paging is disabled, these registers and the table they point to are ignored. If paging is enabled, then these two registers define the current page table, which is used during address translation. An operating system may store other page tables in memory, but these are ignored by the hardware. Only the current table counts and it is only used if paging is enabled.

The format of an entry in a page table is given by the following fields:

The frame number serves to address the frame in physical memory. 19 bits can select one out of 512K frames. (Each frame is 8K bytes. This allows addressing any byte in physical memory, since 512K \* 8K bytes = 4G bytes.)

The Valid bit is checked during translation; it must be set to one. If not, a Page Invalid Exception will occur. If the CPU is trying to store into memory, the Writable bit will also be checked; it must be set to one. If not, a Page Read-Only exception will occur. The Referenced bit will be set to one by the MMU when a page is either queried or updated. The Dirty bit will be set whenever a page is updated.

The remaining 9 bits are not examined or updated. The operating system is free to store information in these bits if desired.

When presented with a logical address, if paging is enabled, the MMU will perform the following functions.

First, the appropriate entry from the current page table will be fetched into an internal (hidden and unnamed) register within the MMU. If the Valid bit is zero, a Page Invalid exception will be signaled and no further processing will be done on this instruction. If this is an attempt to store into memory, the Writable bit will be tested. If it is zero, a Page Read-Only exception will be signaled and no further processing will be done on this instruction. If both bits are OK, the frame number will be concatenated with the offset, to give the following physical address:

If this is an illegal address in physical memory, an Address exception will be signaled and no further processing will be done on this instruction. Otherwise, the data will be either fetched from or stored into memory at this physical address. (In the case of the "tset" instruction, a word

will be both fetched and written to the selected address.) The Referenced bit will then be set to one and, if data was stored into memory, the Dirty bit will also be set to one. All other bits will be unchanged. Finally, the page table entry will be written back to memory from the internal MMU register.

The BLITZ architecture is designed to accommodate shared memory multiprocessing, although it will be mostly used as a uniprocessor. With shared memory multiprocessing, several concurrently executing CPUs will share a single physical memory. Multiprocessor interaction and frame locking are discussed next.

Note that when the CPU generates a single memory operation (for example, an instruction fetch) there are actually several reads and writes performed on main memory. A typical memory access will include (1) a read from the page table, (2) a read and/or write to the target frame, and (3) a final update to the page table. Technically, the write back to the page table entry will occur before the actual target location is queried or updated.

In the case of a multiprocessor system, we have the possibility of interleaving of memory accesses from several processors. For example, one processor might conceivably change a page table entry that is being used by another processor.

There are several design choices in how the various memory operations are interleaved in a multi-processor system. Here are several options that were considered in the design of the BLITZ architecture.

First, an architecture might specify that the memory accesses are done independently, with no coordination or synchronization. The only thing that would be done atomically is the read-write pair performed by the "tset" instruction. Unfortunately, with this design option, it is possible that a page table entry may not be updated correctly. For example, assume that some page table entry has its Dirty bit clear. Assume two processors both fetch the same entry, more or less simultaneously. Next, one processor updates the entry first, writing back an entry in which the Dirty bit has been changed to one. Then, the second processor writes back its version of the entry, in which the Dirty bit is still clear. The problem is that the update to the Dirty bit is lost. This is clearly unacceptable.

Second, an architecture might specify that all memory accesses (from (1) the initial read from the page table, through (2) the read and/or write to the target frame, and to (3) the final update to the page table) will be executed atomically, without interference from other processors. This could be implemented by locking each of the page frames involved. Up to two frames may be involved in a single CPU-initiated memory operation: the frame containing the page table and the target frame containing the data to be fetched and/or updated. If the architecture specifies that a processor will first get a lock on the frame containing the page table entry and then will try to get a lock on the frame containing the data before releasing the first lock, there is the possibility of deadlock. Two processors could each hold a lock on their first page while waiting to acquire a lock held by the other processor. Another serious problem with this design option is that for every single memory operation, the MMU holds a lock on a frame containing a page table entry longer than absolutely necessary, and this could slow performance whenever two processors try to run in the same logical address space.

In the BLITZ architecture, a lock is associated with each frame in memory. The lock on a frame may be acquired and released by the MMU during its operation. To perform a memory access, the MMU will first obtain a lock on the frame containing the page table entry, waiting for other processors to release locks on this frame, if necessary. The MMU will then fetch the page table entry, update it, determine if any exceptions will be signaled, write the entry back, and release the lock on the frame. Only after the lock is released, will the MMU perform the memory

operation to the target address. Then, if necessary, a lock will be acquired on the second frame (containing the target address) with the CPU waiting again, if necessary. Finally, the memory operation will be performed and the second lock released. If the operation is to fetch a word or a fetch a byte, or update a word, the second lock (on the target frame) may be unnecessary if all transfers to and from the memory are in units of 32-bit words. If the memory operation is the "tset" instruction, a second lock on the target frame must be acquired. If the memory only moves data in units of words, then an update to a single byte (e.g., the "storeb" instruction) will require a lock on the target frame as well, since an entire word must be fetched, the selected portion of the word updated, and the entire word written back to memory. Without using locks, it is possible that a second processor simultaneously updating a byte in the very same word will cause one of the updates to be lost, which is clearly unacceptable.

Note that the "fload" and "fstore" instructions read and write a doubleword (8 bytes) at a time. The "fload" instruction fetches a doubleword from memory and places it in a floating-point register. The "fstore" instruction copies a doubleword from a floating-point register to memory. In both instructions, the doubleword is moved in two separate steps, which each move a word (4 bytes). There is no locking between the two word-length operations. In a multi-processor system, there may be interleaving of these operations. As an example, consider two processors simultaneously attempting to store different doublewords into the very same address; it is possible that the words are stored in such a way that the final two-word result gets its first word from one processor and its second word from the other processor, due to interleaving of memory operations.

## **Exceptions Common to All Instructions**

Note that all instructions may cause the following exceptions:

Page Invalid Address Exception

When an instruction is fetched, a word from memory must be read to obtain the instruction. If Paging is enabled, then the processor will first consult the Page Table to determine which frame in memory contains the data. If the page containing the instruction is not currently in memory, a page fault will occur, resulting in a Page Invalid exception.

Regardless of whether or not paging is enabled, a physical address will be produced before the instruction word is fetched. If this physical address points to a word that is not in the memory supplied on the specific machine (for instance, the memory address exceeds the amount of installed memory), then an Address Exception will occur.

Since these two exceptions may occur for every instruction, they are not listed separately under each instruction. However, if either of these exceptions could also be caused by attempts to fetch or store operands, that exception is listed explicitly.

Also, any of the asynchronous (hardware) interrupts or the ExceptionDuringInterrupt may occur during any instruction, so these are not listed individually for each instruction.

## **Alignment Exceptions**

Every BLITZ instruction is 32-bits long and must be stored in a word-aligned address in memory.

There are several ways that different architectures may enforce such an alignment restriction. The design options are: (1) Check for alignment on every instruction fetch and have Alignment Exceptions always possible. (2) Check for alignment whenever the PC is loaded (e.g., for the "jmp", "call", "bxx", and "reti" instructions) and have an Alignment Exception only for these instructions. (3) Never check for alignment; simply ignore the last 2 bits whenever the PC is loaded or used.

Option (1) requires the overhead of checking the PC on every instruction fetch. This is often wasted effort: if the previous instruction did not cause an Alignment Exception, then the next sequentially fetched instruction cannot possibly cause an exception. Option (3) requires the least overhead: since nothing is ever checked, an Alignment Exception will never occur.

The BLITZ architecture uses option (2). Any instruction that loads the PC will cause an Alignment Exception if the value being loaded into the PC is not divisible by 4. Due to a bug in some user program, it is possible that an attempt will be made to branch to an address that is not the address of a valid instruction sequence. If the bad address happens to be unaligned, it will cause an Alignment Exception and the kernel can then abort the program. (Of course it is possible that an erroneous target of a branching instructions happens to be aligned properly, in which case instruction execution will continue. What happens next depends on what data happens to lie at the target address.)

Several instructions query or modify data in memory. Some instructions move bytes and other instructions move words. Whenever a word is moved to or from memory, the address must be aligned; if it is not, these instructions will cause an Alignment Exception.

The following instructions may cause Alignment Exceptions:

```

load

(Format E)

loadv

(Format E)

store (Format E)

storev (Format E)

call

jmp

bxx

push

pop

reti

ret

tset

readu (Format E)

writeu (Format E)

ldptbr

ldptlr

fload (Format E)

fstore (Format E)

```

## PowerOnReset and HardwareFault

When first powered on, the BLITZ CPU begins with a PowerOnReset interrupt. At this time, volatile memory may or may not contain meaningful values, and the code that is branched to as a result of the PowerOnReset should lie in non-volatile memory. Typically, this will be "boot" code stored in read-only memory (ROM).

When the BLITZ emulator is used, the memory will be preloaded with a program (e.g., the OS kernel). When execution is initiated (e.g., with the "go" command), the PowerOnReset interrupt processing will occur.